Cocotb

One of the great open source tools in our arsenal that we’ve grown very fond of throughout the years is Cocotb, a very clever framework for simulating HDL (VHDL, Verilog or SystemVerilog) designs. Cocotb is maintained and developed by a vibrant community under the stewardship of the FOSSi Foundation, which Antmicro has been supporting both through sponsoring the excellent ORCONF and related events (we’re hoping to meet you at WOSH in Zurich next week!) and through the personal participation of Antmicro’s CEO, Peter, as a FOSSi Director.

Cocotb simplifies the implementation of complex testbenches and provides functionalities for automatic design testing. Cocotb tesbenches are implemented in Python, which is a very productive language (with a much wider adoption than all of the HDLs combined) that provides a plethora of libraries and functionalities which come in handy when writing more complicated testbenches.

Cocotb itself does not simulate the designs, but rather uses external tools to run the RTL simulation - there is a wide variety of simulators to choose from, including proprietary and open source options. But so far Verilator - another one of our tools of choice (that also integrates with our Renode functional simulation framework) - has not been on that list.

Verilator

Verilator is one of the fastest Verilog simulators on the market, and a fairly old member of the growing family of open source EDA tools. It does not simulate the designs directly, but rather emits a C++ model of the design, a so-called verilated model. The model can be included in a C++ application which acts as a testbench and implements all the simulation logic. If you haven’t heard about it yet, we’ll leave it to Verilator’s own Wilson Snyder to convince you how great it is in his ORCONF 2018 presentation.

Cocotb Verilator integration

Related to our joining of the CHIPS Alliance, an organization which aims to push for verified end-to-end open source silicon designs based on open tooling, together with our fellow CHIPS Alliance and RISC-V Foundation member Western Digital we were looking at how to foster collaboration across different but neighbouring communities, and integrating Cocotb with Verilator seemed like an ideal pick.

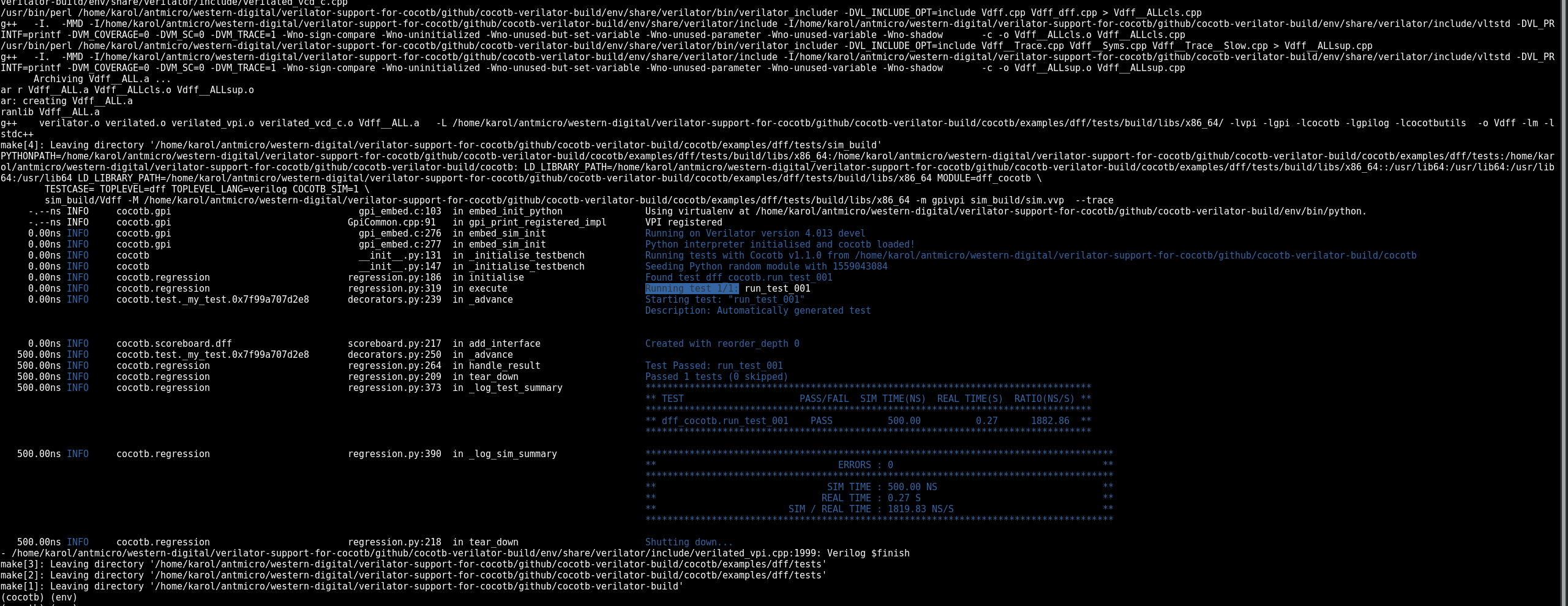

Based on the earlier work of and in collaboration with FOSSi Foundation’s fellow director, Stefan Wallentowitz, and through the kind sponsorship of Western Digital, we implemented a robust and tested Cocotb and Verilator integration - pending upstreaming. Cocotb will now be able to generate a generic C++ testbench of the verilated design, build and run it, using VPI to control the simulation process.

Getting started with the project is really easy. Just clone the top-level repository from Antmicro’s GitHub account (soon to be transferred to the CHIPS Alliance): https://github.com/antmicro/cocotb-verilator-build and follow the instructions from the README file.

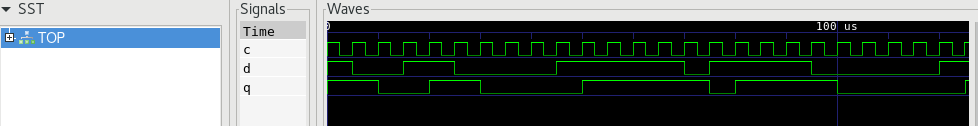

One of the features supported by the Cocotb Verilator integration that we added is signal trace dumping. This feature can be enabled by setting the VERILATOR_TRACE variable. The resulting trace is written into a vcd file and can be viewed by e.g. the GTKWave viewer.

Now on to upstreaming the work! If you want to find out more, be sure to meet us at WOSH and especially at the Bay Area CHIPS Alliance Workshop on June 19, where our VP Business Development, Michael, will be giving a talk about the integration.