Upstream UVM support in Verilator

Verilator can now elaborate upstream UVM 2017-1.0 - no patches or workarounds required. Learn about Antmicro's recent contributions to Verilator, including support for UVM Cookbook.

READ MORE

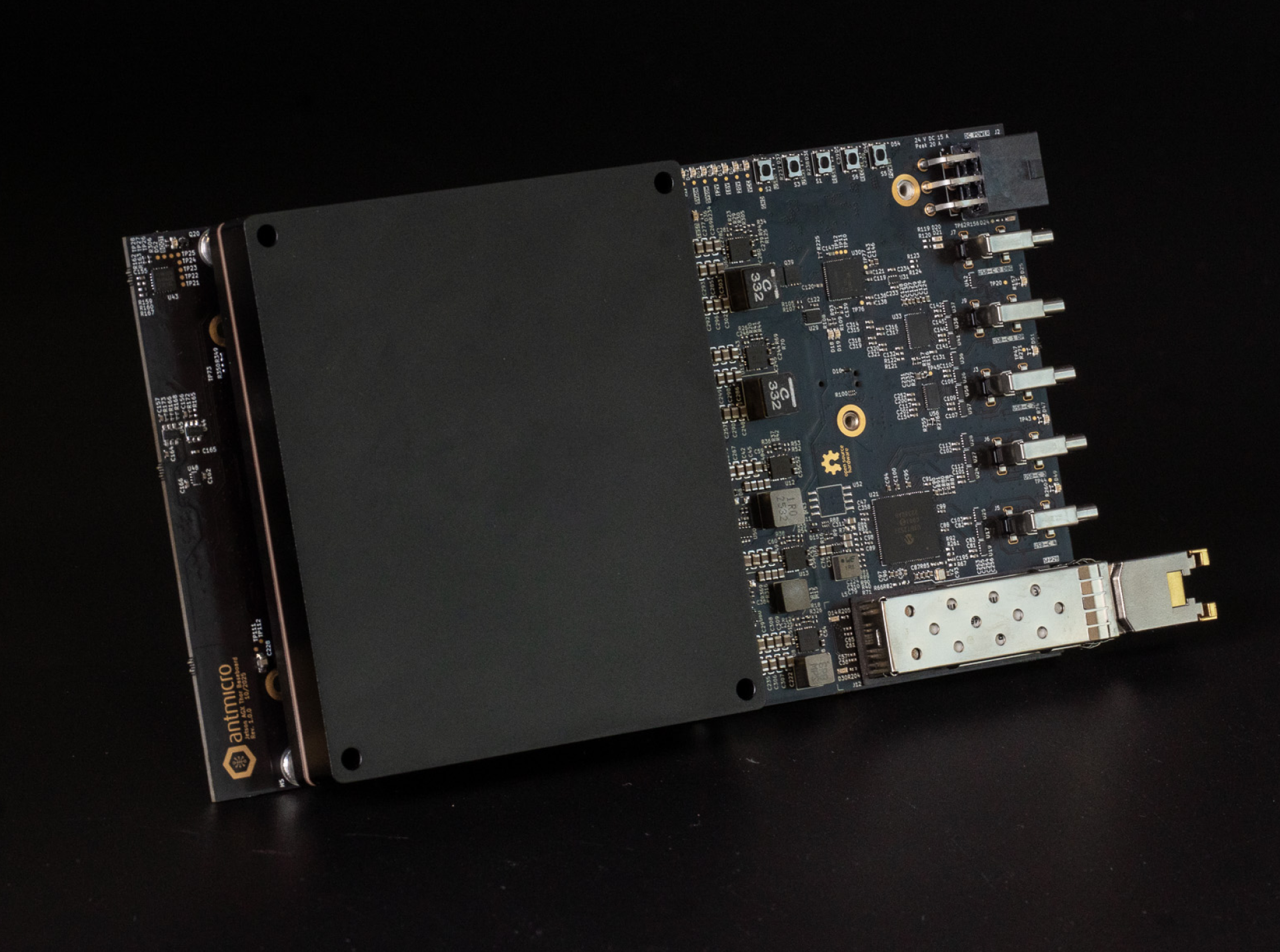

Jetson AGX Thor Baseboard

Our open hardware Jetson AGX Thor Baseboard combined with a custom enclosure can help you accelerate the development of Thor-based products for ruggedized, industrial-grade applications.

READ MORETECHNOLOGY SHOWCASE:

Loading technology highlights...