Antmicro’s open source Renode simulation framework offers support for various instruction set architectures, with the RISC-V ISA being a major focus for both ourselves – as a founding member of RISC-V International – and our customers, including e.g. Google Research and Microchip. Renode’s support for RISC-V is also being developed as part of EU-funded research activities such as TRISTAN, to enable easier prototyping and development of new silicon based on open source core and peripheral IP implementations, which we are also heavily involved with.

Now, further expanding the coverage of RISC-V platforms in Renode, we’re introducing RISC-V bitmanip extensions support to facilitate code size reduction, performance improvement, and energy consumption reduction via fewer and more specialized instructions. In this note we’ll describe the process of enabling RISC-V bitmanip instructions support in Renode, as well as verifying the implementation using Zephyr RTOS.

Tracking RISC-V support with the RISC-V dashboard

RISC-V is a modular ISA, allowing you to select specific instruction subsets and extensions for your core. This is a very good match to Renode conceptually, since the framework is centered around the notion of extreme configurability, including the ability to specify the features supported by a given core or cores in the REPL description of a platform, as well as the capability to support core clusters and heterogeneous setups.

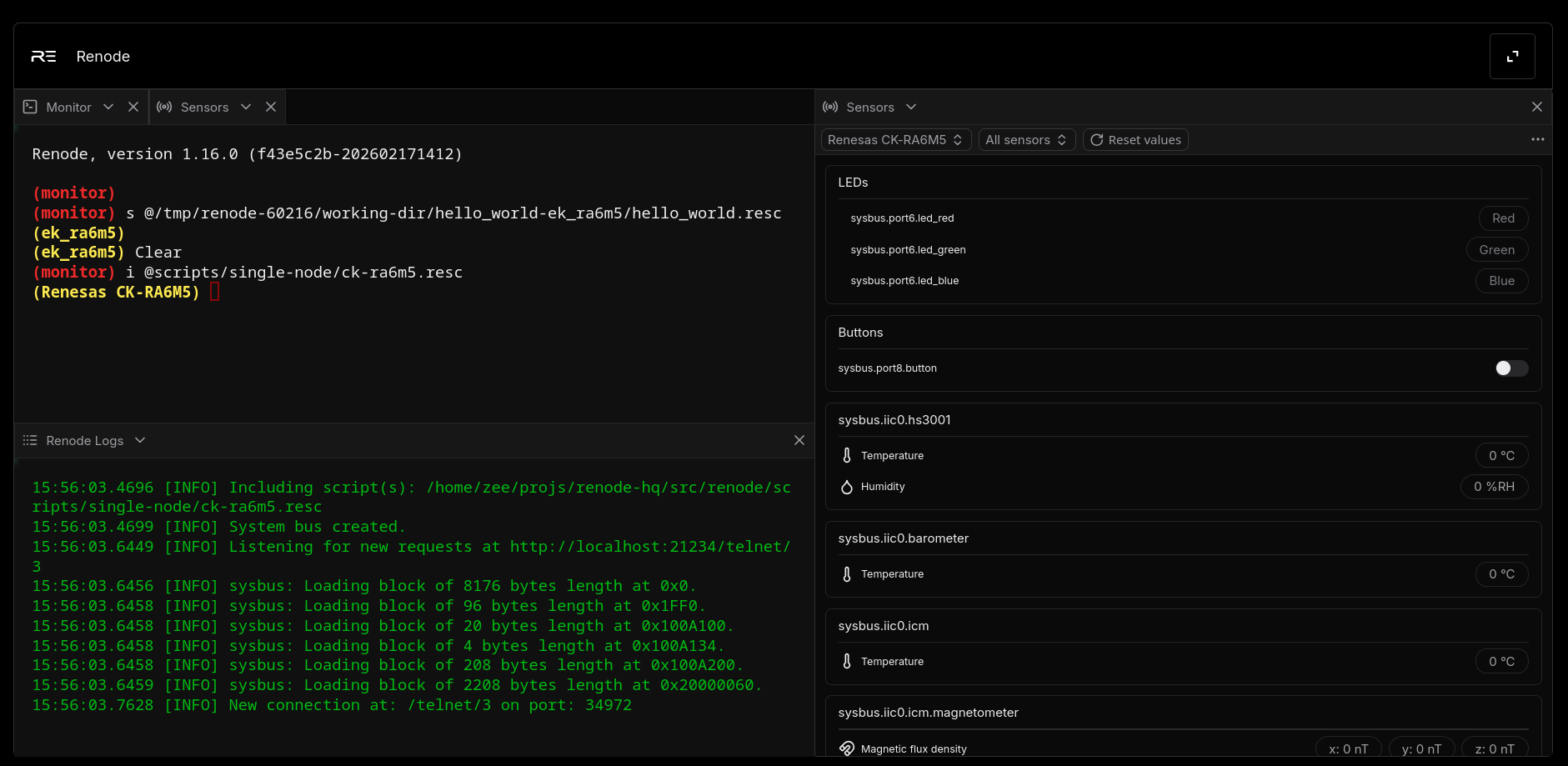

Thanks to the extensive tests as part of our Renode Zephyr Dashboard, a CI system visualizing which Zephyr-compatible boards are currently supported in our simulation framework, as maintainers of the RISC-V ISA in the Zephyr Project we monitor how RISC-V support in both Renode and Zephyr can be improved.

In one such activity, we noticed the test for OpenTitan EarlGrey SoC, which is a platform supported in both Renode and Zephyr, was failing in the dashboard for no obvious reason. Upon investigation, we could attribute this failure to the fact that Zephyr used to only define RISC-V extension configurations in Kconfig files, and not devicetrees, which we used for generating Renode platform files. Since Ibex used in EarlGray does support bitmanip extensions, but this fact was not in any way reflected in devicetree data, our dts2repl tool did not report a problem; the platform was successfully generated and run in Renode, but just did not work. To fix this situation, we reworked how the RISC-V ISA strings are described in Zephyr, making them visible in device trees, which uncovered the missing extension set in the “eyes” of dts2repl, and thus, Renode.

Adding RISC-V bitmanip support in Renode

With a clear indication of the genesis of the failure, we could proceed to get the OpenTitan platform to pass in the dashboard.

To make this happen, we implemented the bitmanip instructions in Renode, and improved the mechanism for defining which ISA extensions should be used in the simulation. In the original RISC-V Privileged Architecture specification, ISA-defined extensions were identified by a single letter (A-Z) and Renode followed this notation in platform descriptions. With the new additions to the RISC-V ecosystem this turned out to be quite limiting, so a new, more descriptive notation was introduced by the RISC-V International. The rv64imac-style notation was extended to allow “Z”-style extensions, and the change is now mirrored in Renode, e.g. now you can use cpuType: “rv64imac_zba_zbc_zifencei”. This new development allows for a more strict definition of selected RISC-V features. As part of this work, we have also extracted the Zicsr and Zifencei extensions, as enabled separately from the base instruction set.

With the bitmanip instructions in place, the OpenTitan test case now passes, as can be seen in Renodepedia. We’re also working on adding bitmanip to the RISC-V Torture test generator to provide more tests for our support of this extension.

Renode for RISC-V-based platform development

Renode can help you rapidly prototype new platforms based on RISC-V, especially in ML-focused and security-first scenarios. With the growing coverage of platforms, illustrated by the Zephyr and U-Boot dashboards, Renode offers comprehensive development capabilities for RISC-V and other architectures, also in heterogeneous setups.

To learn more about the benefits of integrating Renode in your workflows or developing your next RISC-V-based project with Antmicro, reach out to us at contact@antmicro.com.