Open source tools and workflows are becoming increasingly capable in the field of ASIC and FPGA development and implementation, especially in niche applications not addressed by the mainstream, proprietary alternatives. Open source PDKs such as the SkyWater 130nm or GlobalFoundries 180nm, released in collaboration with Google, are also meant to help enable formerly unaddressed niches and use cases. In one such commercial project leveraging the SkyWater 130nm PDK, Antmicro integrated an open source CAN controller which can serve as a good reference of these capabilities.

The project’s aim was to develop an ASIC containing a CAN controller and a range of other components, targeted towards the SkyWater 130nm process. Antmicro’s role in the process was to use open source tools to provide a CAN controller for the system based on an existing open source controller IP in VHDL. The solution was developed using the OpenLane flow and Caravel, a template SKY130 based SoC. The result of this effort is a wrapper repository which integrates the CAN FD IP core into the SoC via Wishbone and provides additional testing infrastructure and tooling.

In this note, we will walk the reader through the process of integrating an open source core in a larger system and preparing a testing and development environment for a Digilent Arty board using Renode and Verilator, similar to what we have described in the recent Renode MPW Tester note.

Wrapper development and size reduction

In this particular case, the client wanted to implement a CAN core based on an MIT-licensed variant of the CTU CAN FD Controller developed by the Czech Technical University in Prague.

The main features of the CTU CAN FD IP core are as follows:

- Designed to be compliant with ISO11898-1 2015

- RX buffer FIFO of 32 - 4096 words (1-204 CAN FD frames with 64 bytes of data)

- 4 TXT buffers (1 CAN FD frame in each TXT buffer)

- 32-bit slave memory interface (APB, AHB, RAM-like interface)

- Support of ISO and non-ISO CAN FD protocol

- Timestamping and time-triggered transmission

- Loopback mode, bus monitoring mode, ACK forbidden mode, self-test mode

- Interrupts support

- Distributed with a SocketCAN Linux driver

One of the key elements of the work was building the Wishbone to native wrapper contained in the main repository project, which we developed using the Migen open source hardware design language.

As the OpenLane flow primarily supports Verilog, another task required for the integration was converting the IP core itself from its original VHDL source to Verilog through the GHDL yosys plugin for VHDL analysis, compilation and simulation.

After the Verilog conversion, we needed to make sure the CAN IP core’s would fit both in the Xilinx Artix-7 FPGA family based test and development system, as well as the target ASIC area. To achieve that we had to modify the size and number of the core’s RX FIFO and TXT buffers to minimize the silicon footprint.

Simulation and in-system testing

With all these pieces in place, to make sure the core actually works for the specific use case, we created a simulation and testing setup that could be used for verification. The CTU CAN project itself provides several simulation test benches for testing the IP core’s operation. Parallel to the VHDL to Verilog conversion, these tests were adjusted to take into account the size-related modifications mentioned above, and run to verify the core’s correct functioning. Subsequently, Antmicro created an additional set of verification tests using the cocotb framework as a means for testing the CAN core in various use-case scenarios where the core is connected as responder to the Wishbone initiator.

To provide better verification coverage, the CAN IP core was then co-simulated in Renode as part of a larger system containing a processor and other peripherals, making it possible to verify that all ports on the core were functional.

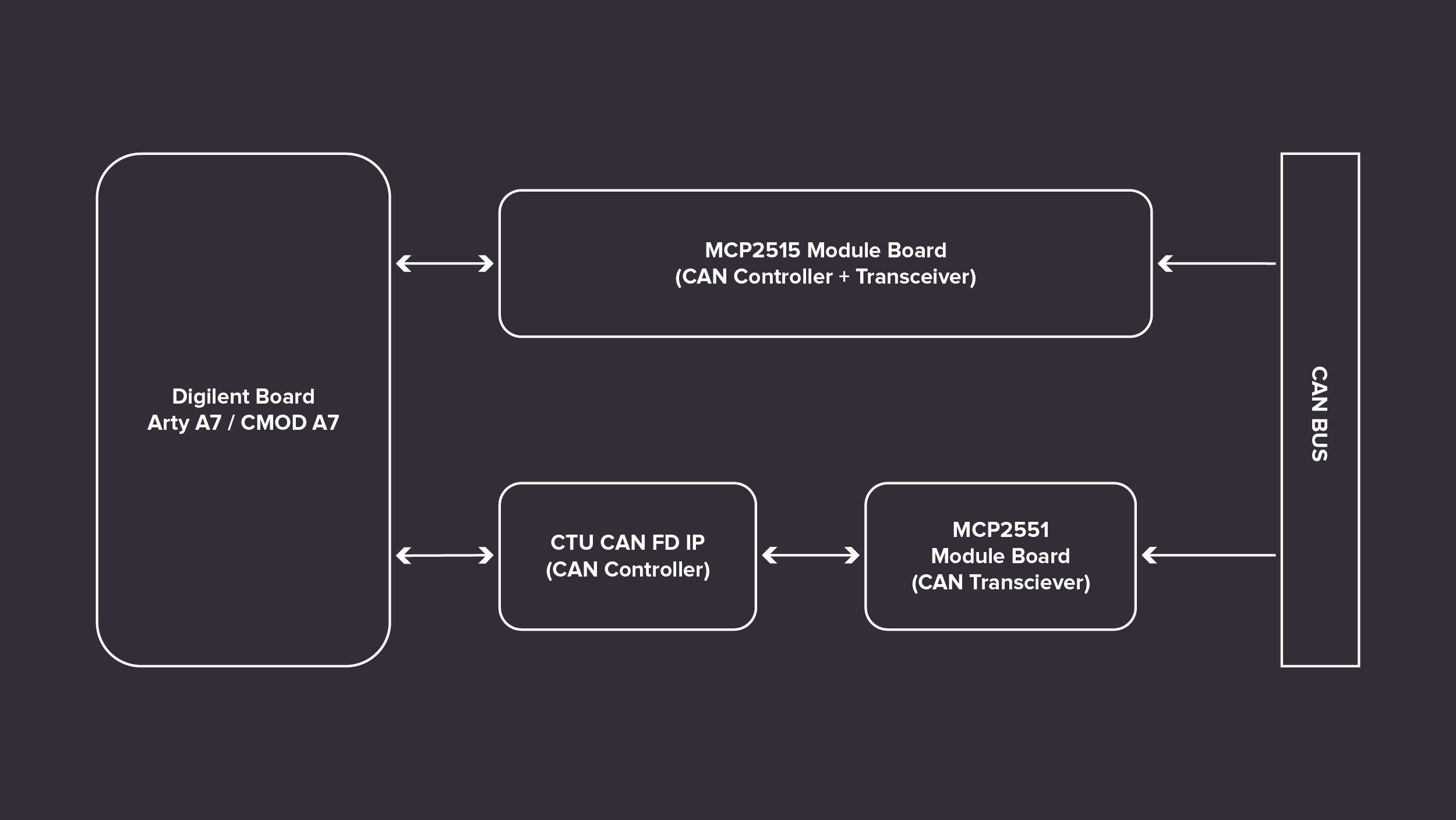

For in-system testing, Antmicro created an FPGA-based system running Linux using Linux On Litex-Vexriscv, targeted for the Digilent Arty A7 board. On top of that a test setup was built connecting the CTU CAN IP-core with an external MCP2551 CAN transceiver board on one end and an MCP2515 module board on the other. Both ends were a part of the same platform for simplicity’s sake, resulting in a looped CAN transmission. The setup is illustrated below:

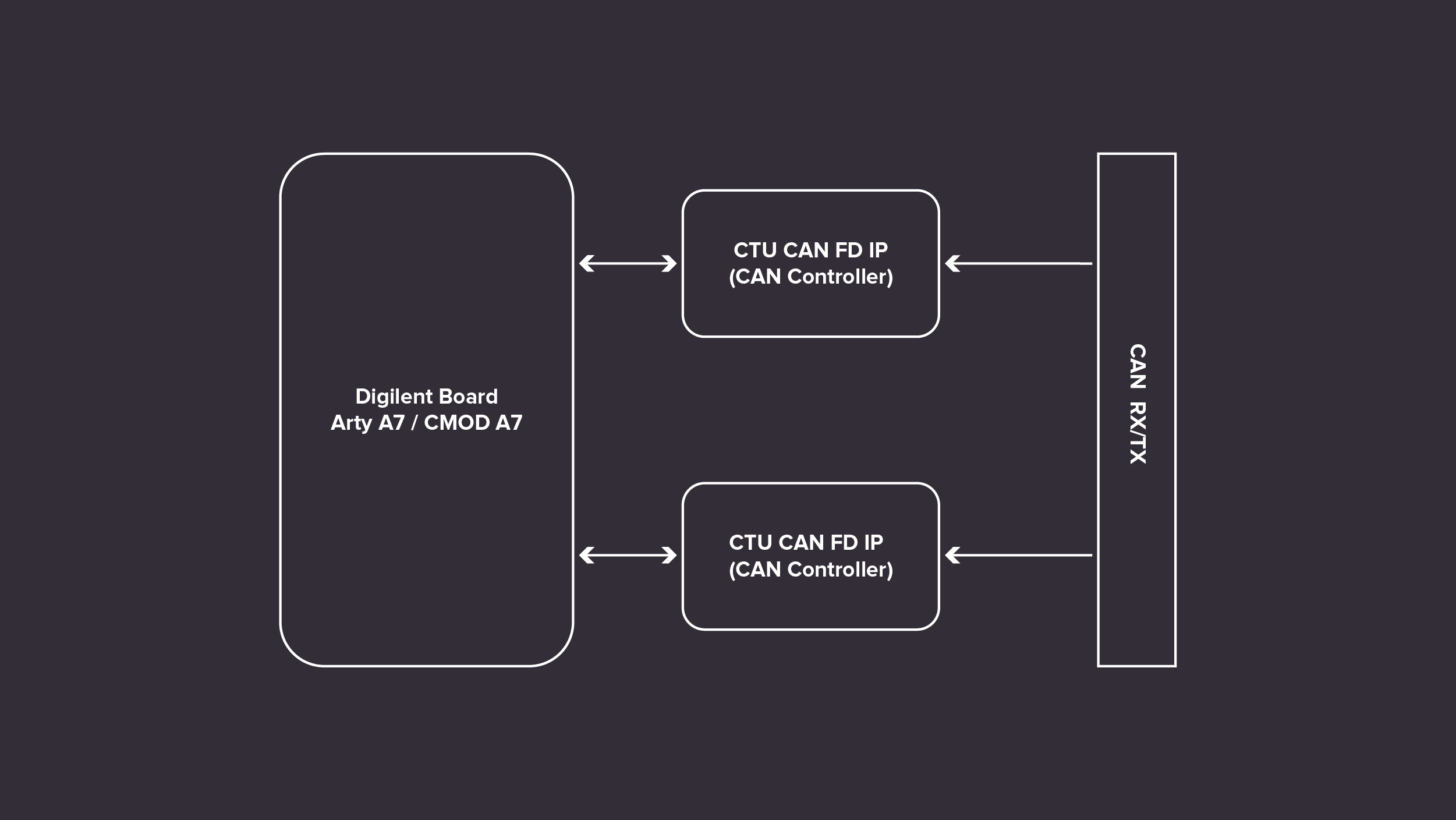

The setup presented above, however, does not support the CAN flexible data rate standard (CAN FD), so another setup was built to test this particular functionality. In this setup, the transmission lines of two CTU CAN IP cores are connected directly:

What is worth mentioning, even though the patents related to the original technology have expired, Robert Bosch GmbH of Germany holds patents and the trademark for the CAN FD protocol, and any commercial implementation may be subject to a license fee.

Next, a simple application was also created for the purpose of repeating the tests performed in the cocotb simulation on hardware and ensuring the reproducibility of the results.

Open source future of ASIC development

As demonstrated by this project, open source IP cores can be successfully integrated for ASIC use, using exclusively open source tools for design, simulation, building and testing. This is indicative of how capable open ASIC and FPGA development workflows as well as simulation and testing capabilities have become thanks to initiatives such as RISC-V International and CHIPS Alliance, where Antmicro has been playing a key role.

If you are interested in IP core integration into ASIC or FPGA solutions, simulating complete ASIC designs in Renode, or you would like to find out more about open source ASIC workflows and their capabilities, feel free to reach out to us at contact@antmicro.com.