Developers of IoT and embedded systems often have to deal with the considerable inconvenience of manually re-plugging and re-flashing a number of boards and components to test various scenarios, firmware versions and setups. This requires access to large amounts of physical hardware and is a convoluted process. Facing the exact same hurdles and looking for ways to make our work more efficient, we at Antmicro developed Renode - a framework for simulating physical hardware: from CPUs, peripherals, sensors, environment, to wired or wireless medium between nodes.

Over the years, Renode has matured, extending its functionality with every release and gathering a strong following of developers who have been successfully using it for their purposes. Recently, the framework has reached an important milestone with its 1.9 release, which comes with support for new platforms, a range of RISC-V-related improvements, and a host of other useful additions, fixes and changes.

New RISC-V platforms and improvements

Renode constantly develops its support for the RISC-V ecosystem. The 1.9 release introduces support for Privileged Architecture 1.1 and Kendryte 210 - an AI capable RISCV64 dual core SoC, as well as Supervisor level support for the VexRiscv FPGA-optimized RISC-V implementation, better customizability of RISC-V cores, a wide range of improvements to various peripherals in the LiteX SoC builder ecosystem and improved support for a range of platforms.

We have also enhanced the support for the LiteX framebuffer, preparing a dedicated demo of Linux with framebuffer targeting LiteX on the NeTV2 open video development board. Moreover, the framework’s co-simulation capability has been expanded with new Wishbone support for verilated peripherals. This allows you to integrate your IP within the simulated environment easily, without having to create Renode models. The newest release includes a demo with the Zephyr RTOS running on LiteX/VexRiscv with a verilated UART.

OpenPOWER

The POWER Instruction Set Architecture has joined RISC-V as the second major open source ISA supported by Renode. Our framework now contains a platform and demo based on IBM’s first open source POWER implementation called Microwatt, running MicroPython. The introduction of the POWER ISA support in Renode means that our simulation framework is ready for more open source CPUs based on this architecture that are expected to be released in the future.

Dual radio support

Another interesting development that the 1.9 release comes with is support for Zolertia Firefly - a breakout board which features two Texas Instruments’ radios able to bridge networks operating at the frequencies of 2.4 GHz (CC2538, with integrated MCU) and 868 MHz (Sub-GHz - CC1200). It is an interesting IoT platform which showcases Renode’s capability to develop and test complex, multi-protocol systems with ease, and we are planning to publish a separate blog note dedicated to this topic soon.

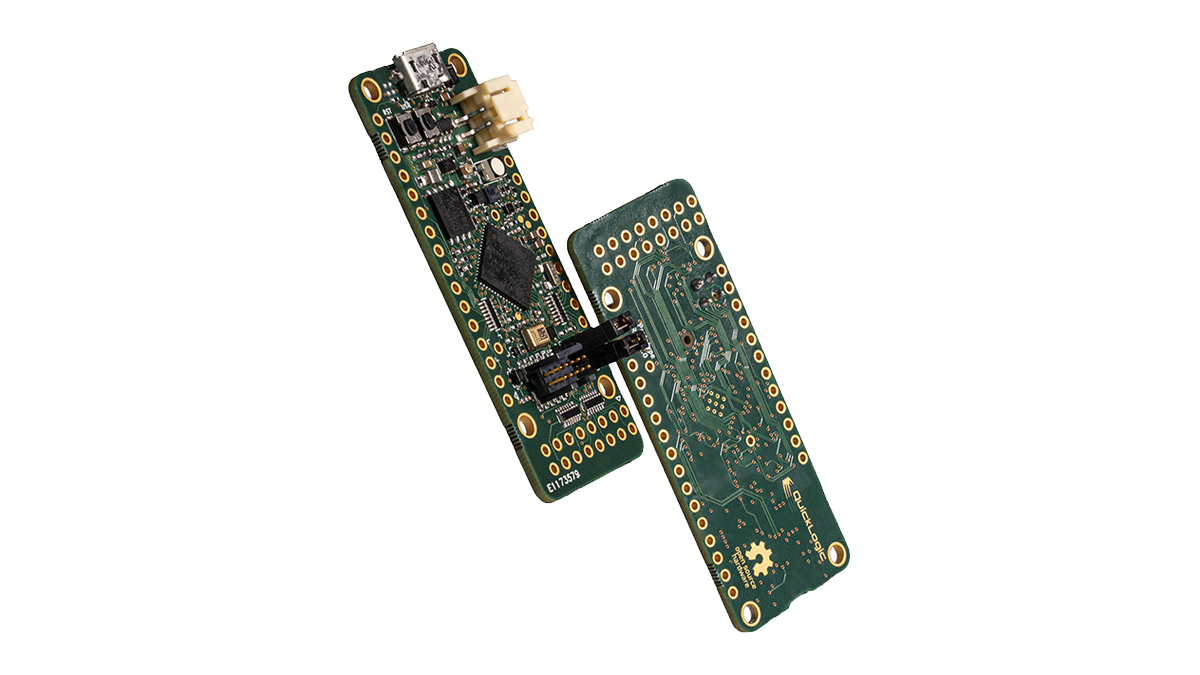

Open FPGA QuickLogic development boards

Apart from Zolertia Firefly, Microwatt and Kendryte 210, the bunch of newly added Renode-supported platforms includes QuickFeather and Qomu boards featuring the EOS S3 SoC from QuickLogic, which has recently become the first FPGA vendor to embrace open source FPGA development tools by contributing crucial data to SymbiFlow - a collaborative project involving Antmicro, Google and a growing community of developers. Additionally, Antmicro ported the Zephyr RTOS the EOS S3 chip, with Renode samples provided for QuickLogic’s boards.

Online momentum

Renode is generating quite some buzz online, reflected in a few articles that have popped up since its most recent release. Memfault, a company providing firmware diagnostics services, has successfully used our platform and has written about running their firmware on it - an interesting read if you want to learn about Renode from a user’s perspective.

Based on our successful collaboration, PlatformIO added documentation for Renode’s integration with their framework for embedded applications, and Carlos Eduardo de Paula from RedHat wrote an excellent guest note on the Zephyr Project blog about using all three together - Renode, PlatformIO and Zephyr.

Summary of most notable updates

If you already are a Renode user, note that in version 1.9 the Renode configuration directory was moved to another location. To use your previous settings and Monitor history, you will need to start Renode 1.9 and copy your old config folder over the new one. On Linux and macOS the directory has been moved from ~/.renode to ~/.config/renode. On Windows it has been moved from the Documents folder to AppData\Roaming. Those changes are in line with the default locations of the config files in the respective OS.

List of selected upgrades:

Added:

- support for RISC-V Privileged Architecture 1.11

- EOS S3 platform, with QuickFeather and Qomu boards support

- EFR32MG13 platform support

- Zolertia Firefly dual radio (CC2538/CC1200) platform support

- Kendryte K210 platform support

- NeTV2 with LiteX and VexRiscv platform support

- EFR32 timer and gpcrc models

- MAX3421E USB controller model

- support for Wishbone bus in verilated peripherals, exemplified with the riscv_verilated_liteuart.resc sample

- scripts to create Conda packages for Linux, Windows and macOS

Changed:

- VexRiscv now supports Supervisor level interrupts, following latest changes to this core

- PolarFire SoC script now has a sample binary, running FreeRTOS with LwIP stack

- NetworkInterfaceKeywords now support wireless communication

The full list of additions, changes and fixes can be found in Renode’s changelog.

If you are developing IoT systems, you might want to consider using Renode to save time, effort and cost by capitalizing on the frameworks’ ability to simulate, test and debug complex, multi-node systems of devices. Write to us at contact@renode.io to find out how exactly Renode can transform your embedded software testing and hardware-software co-development process.