It is becoming evident that the next level of advancement in chip-building can be achieved through open, modular and collaborative methodologies resulting in unmatched flexibility, ease of development and robustness of the end product. This approach is shared by our partners zGlue and Google, with whom we have been collaborating to create a more open and collaborative ASIC design ecosystem.

Continuing to collaborate towards open chips

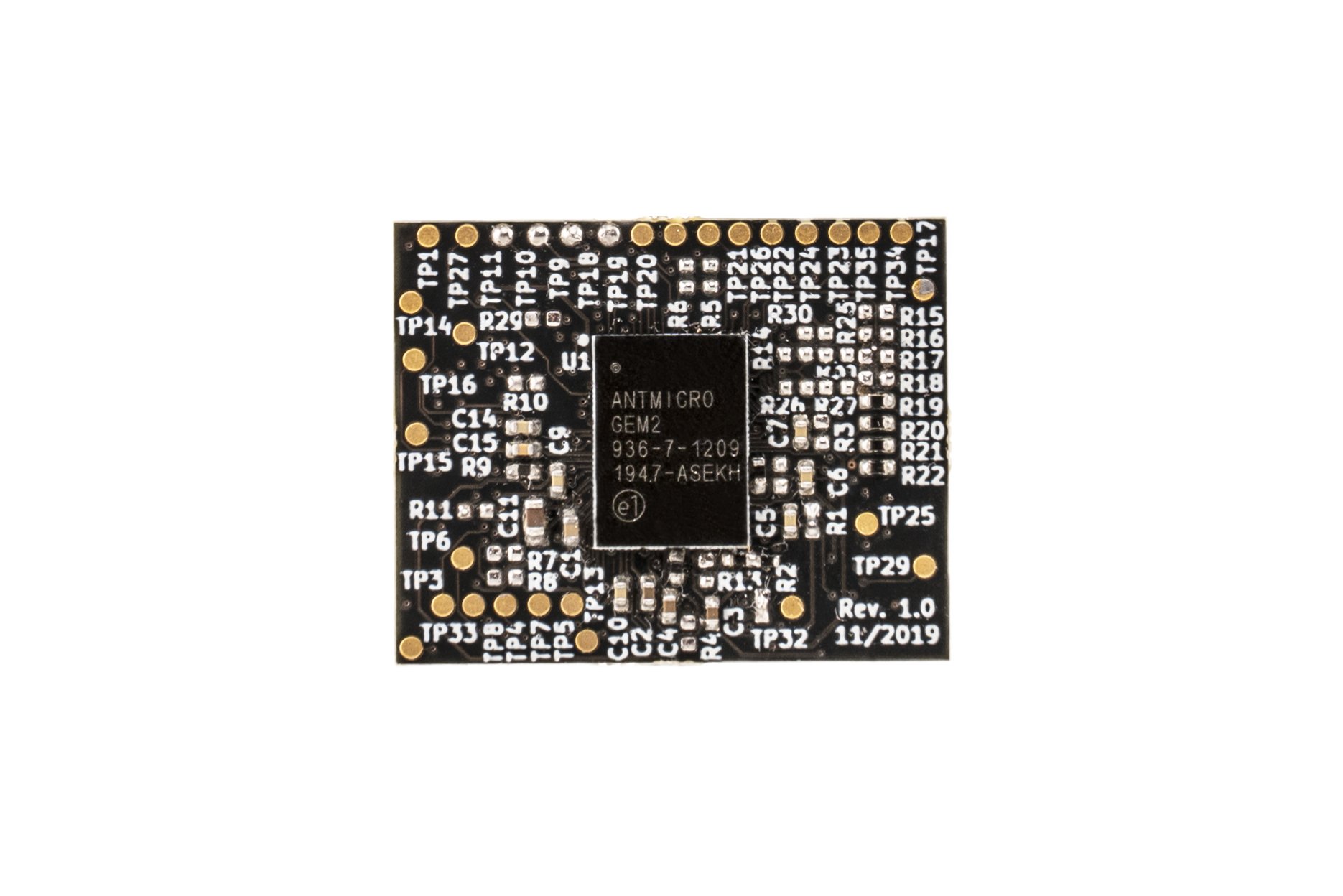

Following our joint effort to build two rapid-turnaround proof-of-concept SiPs (System-in-Package), GEM1 and GEM2, we have teamed up again with zGlue and Google to publish the zGlue Chiplet Info Exchange Format (ZEF) on an open licence, along with a range of open designs and tools. The release is a part of Open Chiplet Initiative, which aims to lower the entry barrier in chiplet-based system design. The tools that have been made publicly available include a bring-up/testing software library (PyChipBuilder), development kits and design examples, including ones for AI use cases, featuring the RISC-V and Arm architectures.

OCI allows our customers to kick-start their development using readily available projects as templates and inspirations. As Antmicro’s contribution to the initiative, we have released the GEM1 and GEM2 designs as open source, along with the associated adapter and devkit PCB designs. This is a step towards an open and modular chiplet ecosystem, where we can collaborate with our customers to efficiently build advanced chips consisting of various heterogeneous building blocks.

What’s the deal with GEM?

Our cooperation with zGlue towards democratizing the chip making process goes back to last year’s release of the rapid turnaround GEM1 SiP, followed by this year’s GEM2. Both were built using zGlue’s innovative smart fabric technology, which makes it possible to freely combine RISC-V and Arm CPUs, FPGA, sensors, etc. GEM1 consists of two Lattice iCE40 FPGA chiplets, one for processing and control, the other for image processing and inference, together with additional circuitry for MIPI switching between passthrough and processing mode. Its younger sibling, GEM2, replaces one of the FPGAs with eFabless’ RISC-V MCU, Ravenna. Both of these designs are tiny, smart and flexible, and could be used as a base for SiPs targeting applications for computer vision, industrial IoT, medical devices and more.

Chiplets are going mainstream and open source

In the chiplet space, Intel is pushing forward with their die-to-die Advanced Interface Bus (AIB) interconnect standard, a technology now governed by CHIPS Alliance. Aiming to break down the design process into smaller chunks, like zGlue does, but targeting much more advanced, higher-cost and higher-bandwidth applications, AIB enables easy integration of multiple building blocks into a single device for SoCs, FPGAs, SerDes, etc. CHIPS has recently announced AIB 2.0 and both Intel and CHIPS are very committed to popularizing the open spec with open RTL implementation.

Future developments

At Antmicro, we are seeing an incredible opportunity in using chiplets to bring ASICs and SiPs to a much broader range of applications by breaking down complexity and reducing cost. One of our recent projects involved RPC (Reduced Pin Count) RAM - an interesting new technology that can have an important impact on chipmaking. RAM is needed to run full-fledged operating systems such as Linux, but is also typically difficult to incorporate into small devices due to its size and the large number of pins. With RPC RAM, which can get as small as 2mm x 4.7mm, a chiplet based design can be created using zGlue’s smart fabric that could run Linux - potentially even in a multi-core setup - in a miniscule footprint.

To enable this kind of exciting developments, we have added RPC RAM support to the open source LiteDRAM memory controller (to be described in a separate note), so that we are able to add RPC memory to our soft - and in the future also hard - processors.

The modular and open chiplet-based chip-building technology significantly reduces the time needed to create functional silicon and broadens its applications. Especially in the context of rising open ASIC development flows and tools such as SkyWater PDK and OpenROAD, chiplet based designs may be extremely interesting in that they allow gradual adoption of open source, software-centric methodologies, unlike monolithic designs.

Antmicro are dedicated to supporting a more agile chipmaking approach and applying it in practical customer applications, so if your project requires a unique, fast-turnaround chip, get in touch with us at contact@antmicro.com.