Antmicro is happy to announce the next, 1.14 release of our open source Renode simulation framework, including lots of new developments originating from both customer and R&D projects, along with community contributions. Since the last release, we’ve passed several important milestones such as adding ARMv8-A and 64-bit peripheral support in Renode and initial support for ARMv8-R. The 1.14 release also introduces Direct Programming Interface support, many new platforms including STM32WBA52 and the RISC-V-based HiFive Unmatched, improvements in a wide range of peripherals, new exciting features and general fixes across the board.

The developments and new platforms introduced in this release also led to major improvements in the Zephyr Dashboard (with more than 290 platforms running!) and consequently, Renodepedia, as well as the new U-Boot Dashboard.

In this blog note we’ll summarize the most important changes brought by Renode 1.14 and describe exciting future developments they enable.

ARMv8-A and ARMv8-R support

The biggest change introduced by Renode 1.14 is support ARMv8-A and ARMv8-R architectures verified using a range of software such as Coreboot, U-Boot and Linux. This enables new use cases with popular ARMv8-A-based CPUs such as Cortex-A53, Cortex-A75, Cortex-A76 and Cortex-A78. Implementing the ARMv8-A GIC controller also involved adding support for 64-bit peripheral registers (named QuadWord) in Renode.

Further expanding its coverage of the ARM ISA families prevalent in embedded systems, Renode 1.14 also includes support for Cortex-R52, the first ARMv8-R processor added to Renode, as described in a recent blog note. This CPU, dedicated for use cases requiring reliable real-time processing, is used in popular MCUs such as Renesas RZ/T2M, NXP S32Z and S32E.

New platforms and peripherals

The new ISA sets and Cortex-A/R SoCs are important, but not the only developments in terms of platforms in Renode 1.14. One of the more interesting additions to the list of supported SoCs is STM32WBA52, a secure Cortex-M33-based 2.4GHz wireless SoC. Leveraging an impressive collection of STM32 platform components already available in Renode and the building-block nature of the framework, we were able to expedite the process of implementing the support for the SoC and the NUCLEO-WBA52CG board that includes it, as described in an earlier blog note.

Other updates in release 1.14 include the addition of RISC-V-based HiFive Unmatched as well as updating the OpenTitan and EarlGrey platform models to a newer version, following the OpenTitan’s RTL freeze in preparation for its tapeout. Thanks to a community contribution, we also improved support for ESP32 chips.

We also filled one important gap in Cortex-M support, adding Memory Protection Unit (MPU) support verified by Zephyr tests.

The new release also involves significant improvements to existing platforms. In collaboration with Google’s ChromeOS team, we introduced major improvements to STM32 platform support, especially STM32F412 and STM32H743. These include new or improved models of ST peripherals such as UART, EXTI, GPIO, DMA, ADC, SPI flash controllers, timers and watchdogs.

The latest release comes with many new and improved peripherals models, including NB-IoT modems, Synopsys DWC ethernet controller or a range of sensors (e.g., SI7210).

Better pre-silicon development and co-simulation with DPI and TBM

Another major addition in the new release is support for Direct Programming Interface (DPI), a standard interface that allows communication between Renode and other HDL simulators that support DPI, for example Verilator, Questa or Vivado’s XSIM.

This change greatly improves Renode’s co-simulation capabilities and opens new possibilities in ASIC and FPGA development. You can read more about DPI support in Renode in a dedicated blog note or Renode’s documentation.

For silicon design teams, another noteworthy feature is support for post-mortem augmented analysis of execution tracing using the Trace Based Model method, alongside Google’s eponymous tool which allows you to get a better read of the performance of your system based on execution logs generated by Renode. This integration lets you estimate the impact of hardware design decisions using automatically generated benchmarks to enable smoother HW/SW co-design.

New and improved tooling integrations

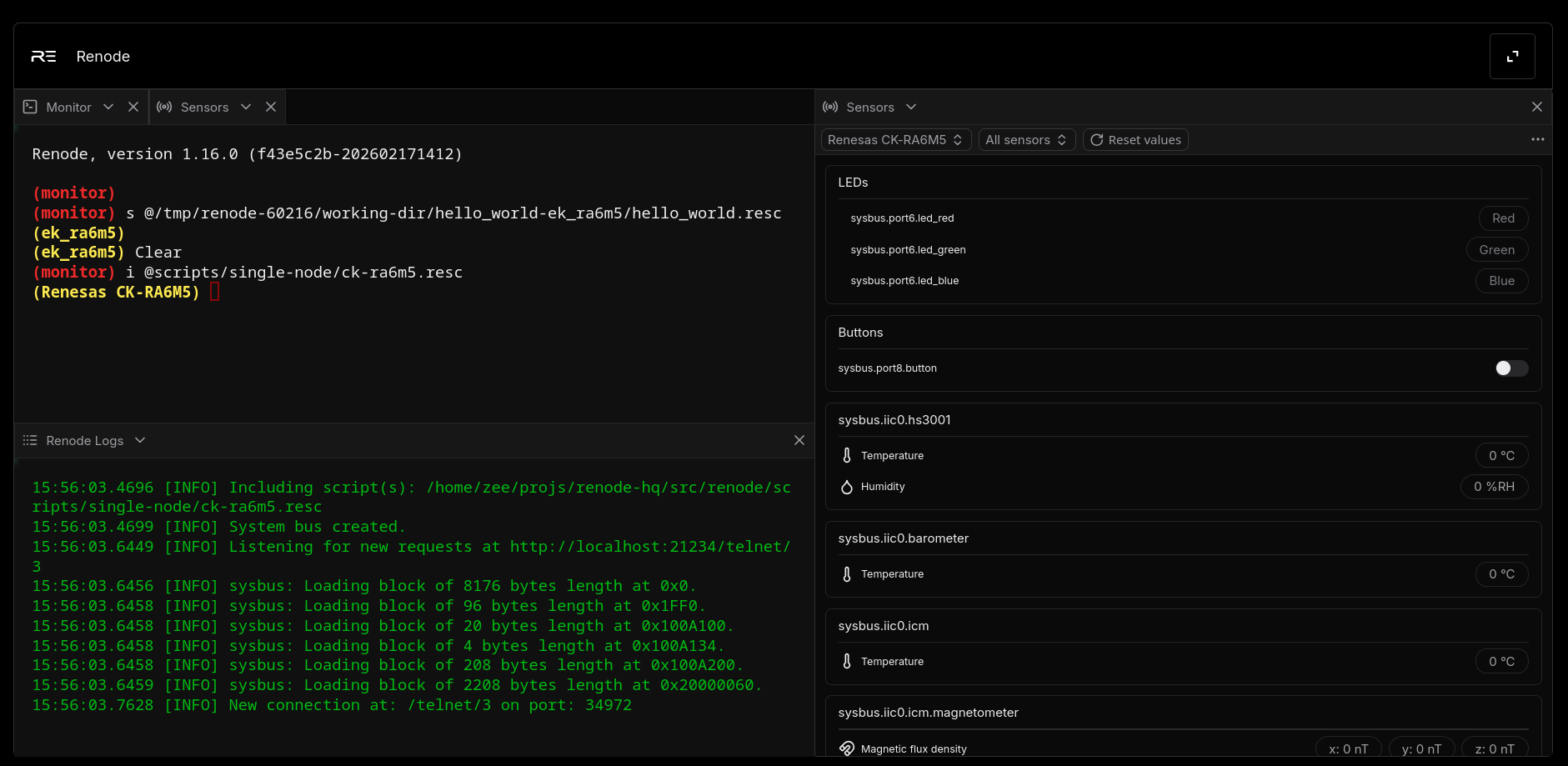

Renode 1.14 also introduces the CSV2RESD tool for generating Renode Sensor Data (RESD) files from plaintext data. The RESD format supports various sensor data types, including temperature, acceleration, angular rate and voltage, as well as custom data samples that can be used to define any model-specific input, and enables concurrent input of multiple sensor data streams into Renode, which is useful in advanced simulation scenarios.

The Renode Robot integration now also features an option to precisely pause emulation when UART or LED events are detected allowing for more detailed verification of time-sensitive test cases. On top of this, the ports used to communicate between Renode and Robot can now be selected automatically.

We’ve also improved the GDB integration layer - it’s now faster and more robust.

Future developments

For a complete list of additions, improvements and fixes, see the 1.14 changelog. There is already a stream of new, exciting developments that didn’t make it into the current release, including initial ARMv7-R and Cortex-R5/R8 support (to be described in a future blog note), or a highly anticipated improved and more powerful Python API.

If you want to add your platform to Renode or are interested in using Renode in your next project for a scalable testing and development environment, don’t hesitate to contact us at contact@antmicro.com.