Zynq mkbootimage: an open source boot image generator for Xilinx Zynq 7000 and UltraScale+

Published:

Topics: Open FPGA, Open source tools

Many years ago, we created an open source tool to assist us in developing new and exciting hardware-accelerated devices with the Zynq 7000 SoC family. The SoC was a novelty at that time, featuring a dual-core ARM Cortex-A9 CPU and a scalable amount of FPGA fabric. This made it an exciting target for many breakthrough projects spanning across the hardware and software boundary that we had had the pleasure of participating in, including the AXIOM 4K camera, the Parallella “supercomputer for everyone” project, or the low-cost Snickerdoodle SoM.

The tool is still in use and actively developed, with new features and support for later and even more advanced UltraScale+ FPGA SoC which did not yet exist at the time it was created. In this note we will describe zynq-mkbootimage and how it allowed us to expand our involvement in open source hardware and FPGA, bringing more software-driven flows into the domain of reconfigurable hardware.

Why we created Zynq-mkbootimage

The Zynq 7000 and UltraScale+ family of SoCs integrate the software programmability and wide array of applications available on the hard ARM-based CPU with the configurable, parallel processing-oriented hardware capabilities of an FPGA. Integrating the CPU and FPGA on a single SoC means that the boot process is a multistage and relatively complex procedure.

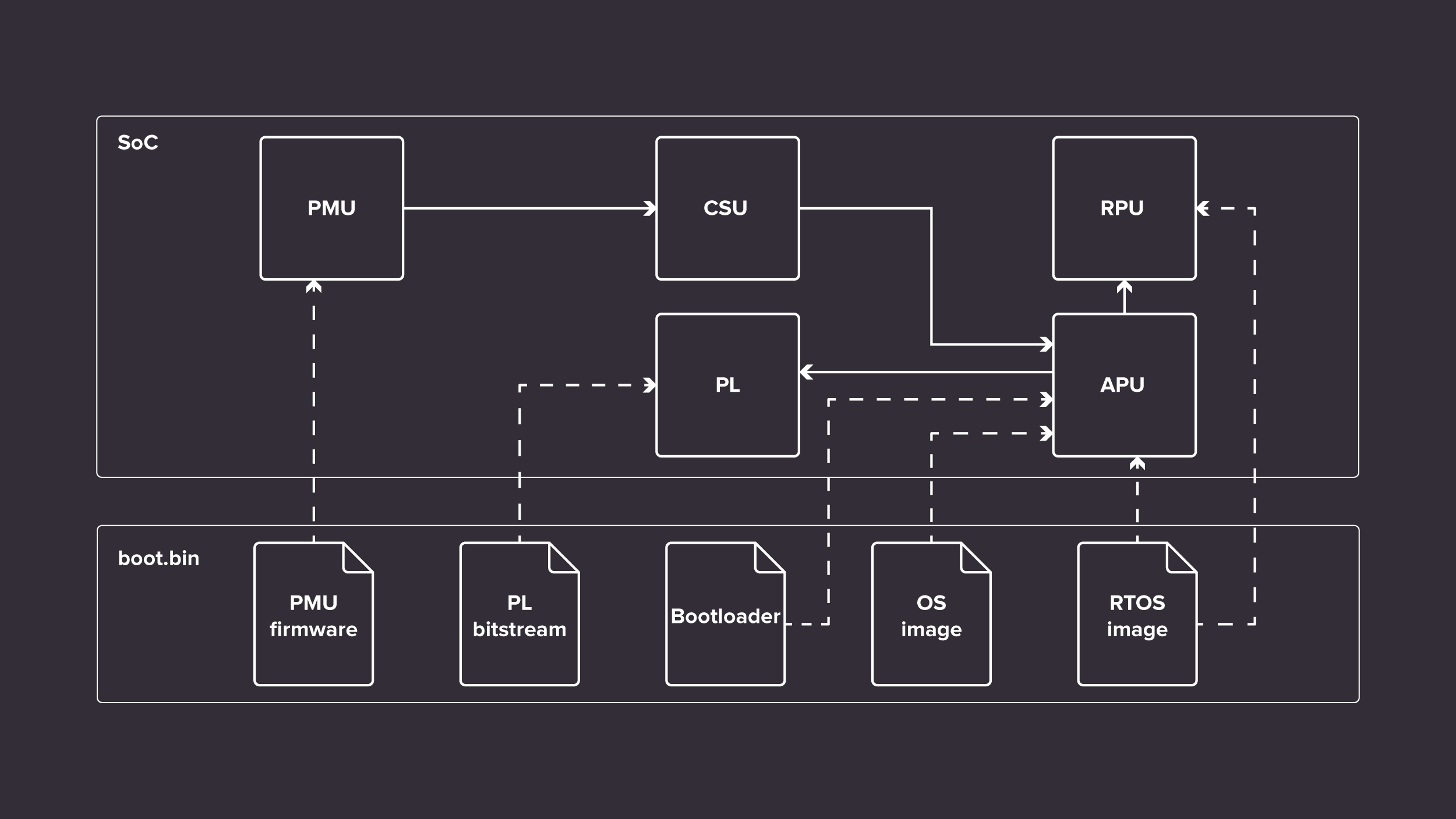

For instance, when an UltraScale+ SoC is powered up, its PMU (Platform Management Unit), which controls all power and reset sequences, passes control to the CSU (Configuration Security Unit). The CSU loads a bootloader into the chip’s memory. The bootloader, in turn, is executed by APU (Application Processing Unit) or RPU (Realtime Processing Unit) and can load an OS to be further executed by the APU unit, or an RTOS for the RPU or a bitstream for the PL (Programming Logic).

The described boot process is depicted in the diagram below:

Designers coming from the FPGA side of the ecosystem will normally use GUI-first tools to generate the relevant FPGA SoC configurations, and they are used to having all their tools (including utilities to generate the boot image as outlined above) distributed in a bundle by the FPGA vendor.

But the breakthrough nature of Zynq is specifically in that it helped more software-oriented developers to employ the low-latency highly parallel nature of FPGAs to accelerate software driven workflows, all while maintaining the familiar ARM + Linux interface so well popularized by the plethora of cheap ARM SBCs and SoMs. This hybrid nature of Zynq enabled many projects we have been working on, such as AXIOM, Parallella and Snickerdoodle mentioned above as well as broadcasting streamers, neural interfaces, stereovision cameras, VR/AR hardware, video-streaming satellite computers and more.

The software-minded developers who wanted to use Zynq would be more likely to prefer command-line driven flows and dedicated open source tools that focus on specific parts of their work - such as gcc, gdb, openocd. This is especially true for things as mundane as putting together a boot image, which you may want to do many times completely independently of complex tasks like bitstream generation, especially if you are developing the ARM side of your FPGA SoC system.

To fill this, gap we created zynq-mkbootimage - a simple, open source, standalone command line tool that combines binaries responsible for different stages of the Zynq boot process, packing them into a single image usually named boot.bin, in the format required by Zynq 7000 and later also UltraScale+ SoCs.

An ecosystem of open tools

The tool is a small but important piece of the larger open source FPGA tooling puzzle, and was early proof that you can introduce more open source workflows into this domain.

It is, of course, constantly being improved and extended with new functionalities like the possibility to unpack previously built boot images or preview their metadata in a human-readable format.

Decoupling the boot image assembly process from the entire FPGA toolchain those years ago helped us work with Zynq platforms in a more effective manner and appreciate the simple but powerful idea of a generic ARM SoC augmented with an FPGA. It paved the way for our further work in creating robust and flexible software-driven CI systems for ASIC and FPGA applications and was a forerunner for our open source hardware efforts which would follow.

Since the time when the first version of zynq-mkbootimage was created, we have engaged with Google, CHIPS Alliance, OpenPOWER and other initiatives to build completely open source tools for software-driven FPGA development. These efforts are now finding their home under the CHIPS Alliance umbrella with some tools already formally onboarded and many more to come.

Making open source FPGA work for you

Our work in the FPGA space is not limited to tools - on the contrary, many of our projects focus on building field-deployed devices based in whole or in part on FPGA technologies. To do this we develop and implement open source IP cores in practical commercial applications, including PCIe, DDR, HDMI, USB, MIPI CSI, SDI, SATA and other interfaces.

We also build a wide array of hardware designs for FPGA-based products, and many of the custom boards we create stem from our internal, open source designs such as the Zynq video board, the UltraScale+ Processing Module and the DC-SCM compatible BMC platform.

If you’re interested in building your next FPGA-based product leveraging our open source, software-driven approach which allows you to iterate faster and increase reuse with open source tools, IP, hardware and software, contact us at contact@antmicro.com to hire our development services.