Antmicro just released its UltraScale+ Processing Module as open source hardware. The release of the UltraScale+ Processing Module joins a long list of open source hardware, industrial grade baseboard designs by Antmicro, such as the successful Jetson Nano / Xavier NX platform, the Zynq Video Board or the recently released Apalis Smart Vision Baseboard.

A closer look at theUltraScale+ Processing Module

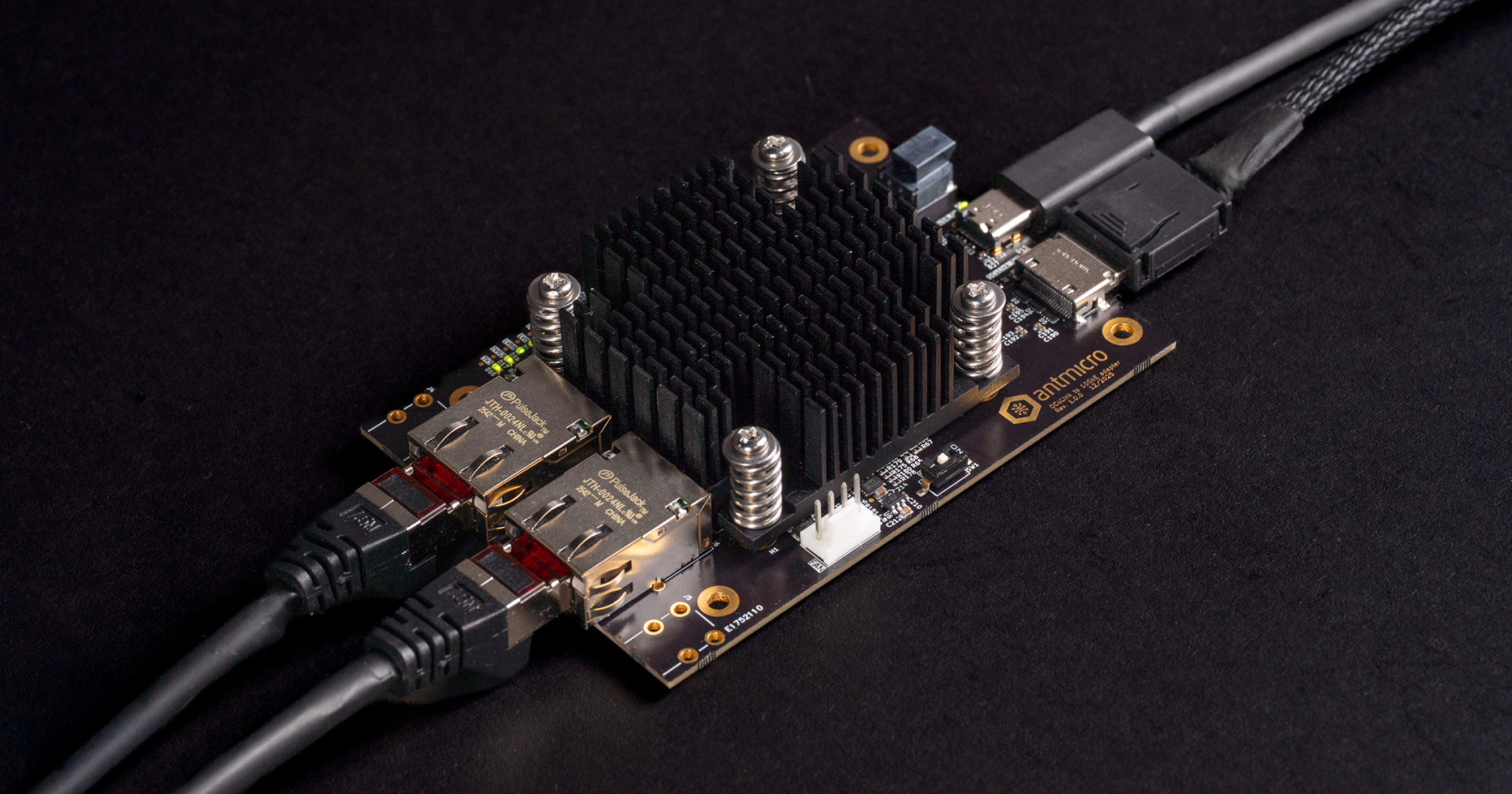

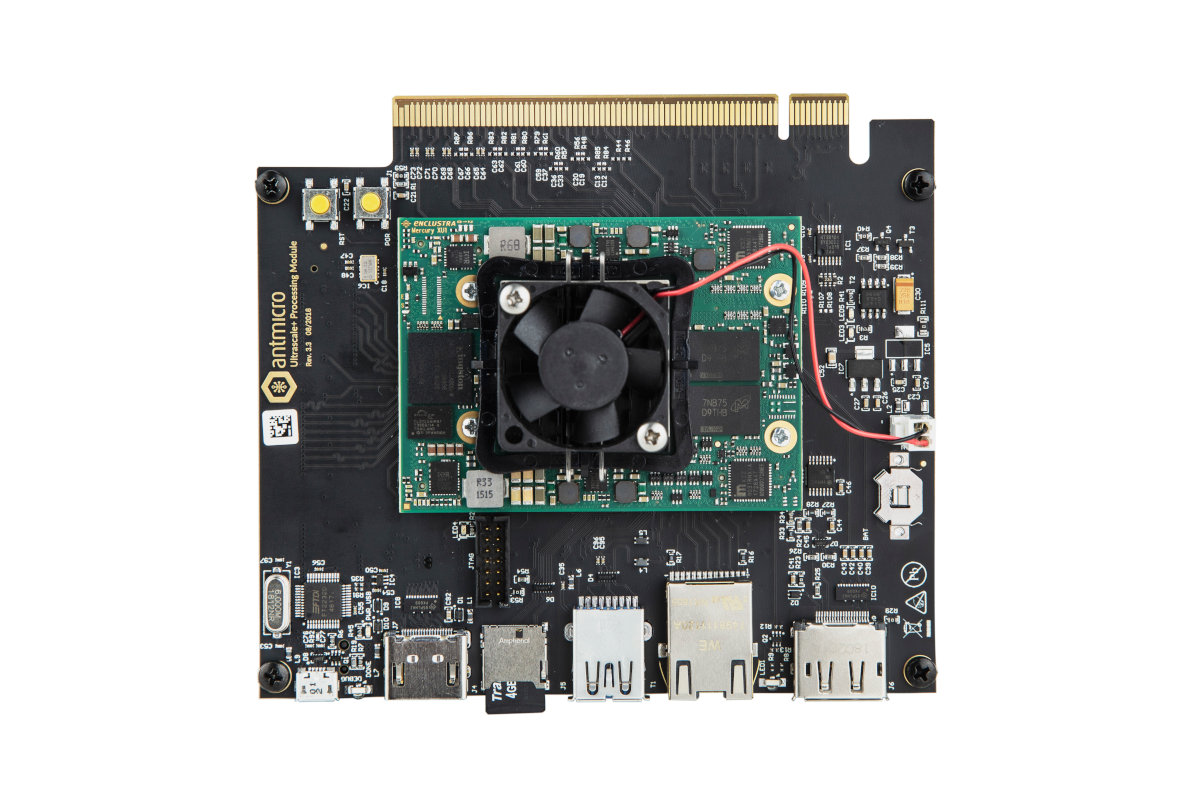

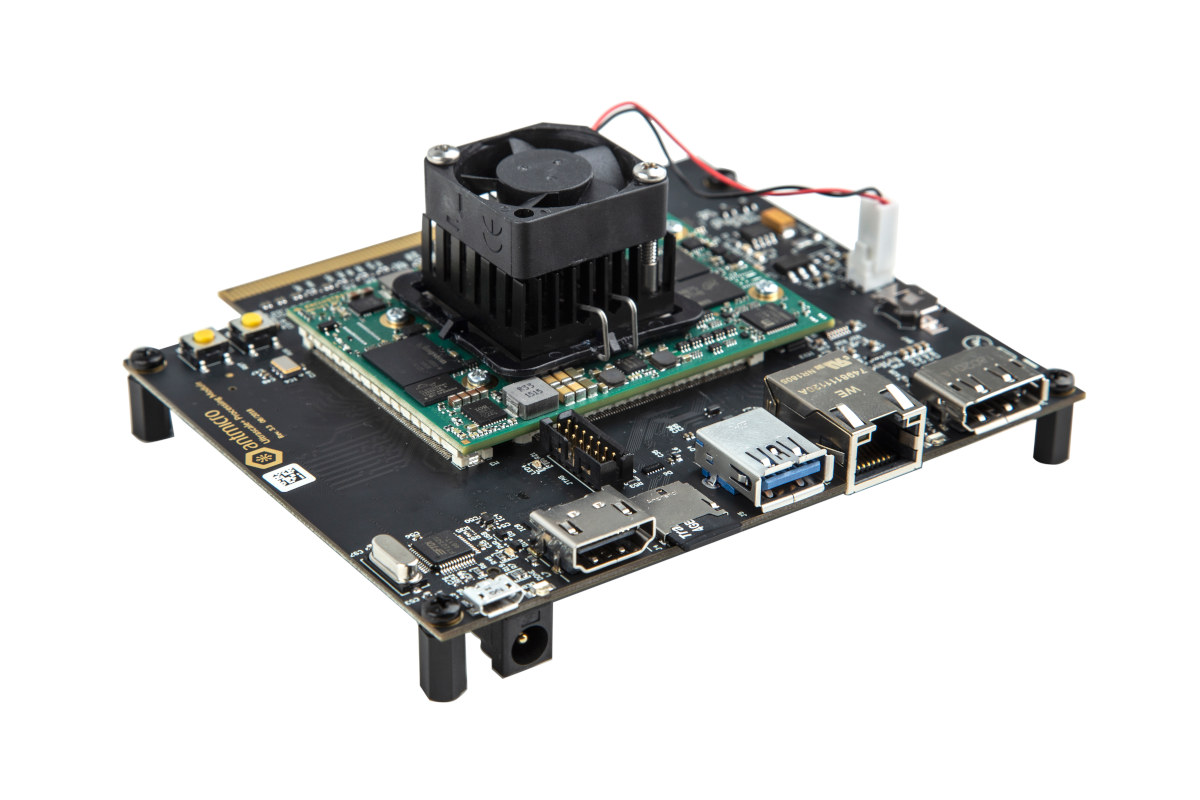

The UltraScale+ Processing Module is a baseboard for Enclustra’s Mercury XU1 Xilinx Zynq UltraScale+ MPSoC modules. It enables to build fast and accurate multi-channel data-acquisition systems suitable for video processing, low latency data streaming for medicine, robotics, and time-critical control systems. The baseboard exposes high-speed interfaces such as Gigabit Ethernet, DisplayPort, HDMI, USB 3.0 and SD card. It also offers 28 differential lanes on a PCIe-style edge connector and 48 I/O pairs available on a board-to-board QSE expansion connector. Those I/O pairs are accessible from the FPGA fabric which allows the user to connect multi-lane, high-throughput sensors and transceivers and harness the full power of the quad core ARM Cortex-A53 CPU on the Xilinx UltraScale+ MPSoC.

One platform - many applications

The platform was successfully used in projects such as the RISC-V based Triple Modular Redundancy demonstrator designed in partnership with Thales or X-MINE, an EU-funded project for real-time identification and tracking of ore in harsh mining conditions. For the latter project, Antmicro developed an industrial 3D depth sensing and tracking platform. The platform includes the UltraScale+ Processing Module, and Antmicro’s TX2 Deep Learning Platform (recently also open sourced) for AI-supported tracking. The 3D camera provides a live stream of the 3D depth maps as well as the position and size of objects tracked on a conveyor belt in a mining setting. The UltraScale+ Processing Module is used in the stereo data acquisition part of the X-MINE 3D camera, and its FPGA firmware designed by Antmicro gathers synchronized data from two high-FPS stereo CMV2000 sensors, transforming it into MIPI CSI-2 and feeding it further to the TX2 subsystem. The 3D camera was designed in a modular fashion so that the UltraScale+ Processing Module could operate both as part of a larger system and as a stand-alone board.

Full-stack FPGA SoC development

One of the major technological focuses of Antmicro is designing advanced FPGA systems based on open source components. The systems we build often include soft SoCs based on open ISAs such as RISC-V and POWER and implement a plethora of I/O IPs for high-speed interfaces. Our portfolio covers IPs implementing the MIPI CSI-2 and other camera interfaces, audio (I2S, SPDIF), PCIe controllers, USB controllers, Ethernet controllers, data movers (DMAs), image Signal Processing blocks (ISP), memory controllers (SDRAM and DDR), 2D graphics accelerators, image encoders and many more. This enables unprecedented flexibility and gives us the possibility of building maximally configurable and portable systems with zero licensing costs and royalties for our customers.

The UltraScale+ Processing Module, now released on GitHub, can be customized by Antmicro for different applications with no strings attached for your end product. In addition to open source IPs, software and hardware, as a Platinum member of the CHIPS Alliance, Antmicro is also developing the open source tooling ecosystems around FPGA, including toolchains, simulation tools, test suites and many more. The systems we build enable Antmicro’s customers to receive complete source code, full insight into the device and full control of the solution.

Visit antmicro.com or get in touch with us at contact@antmicro.com to find out how our end-to-end development services can help you achieve your goals.